2.3.3. Регистры

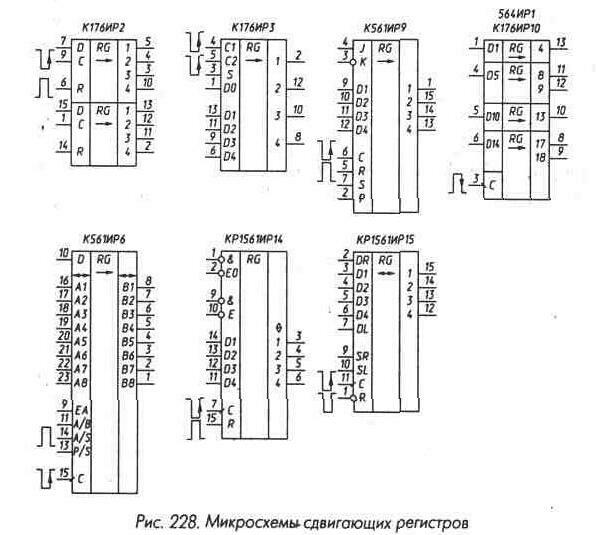

Микросхемы 564ИР1 и К176ИР10 - восемнадцатиразрядные сдвигающие регистры (рис. 228), разделенные на четыре секции с общим входом С для подачи тактовых импульсов.

Секция со входом D1 - четырехразрядная, имеет выход только в последнем, четвертом разряде. Секция со входом D5 - пятиразрядная, имеет выходы в четвертом (8) и пятом (9) разрядах. Секции со входами D10 и D14 аналогичны рассмотренным выше. Запись информации со входов D1, D5, D10, D14 и ее сдвиг происходят по спадам импульсов положительной полярности, подаваемых на вход С. Особенности построения триггеров микросхемы К176ИР10 требуют, чтобы длительность тактовых импульсов не превышала 30 мкс.

Микросхема К176ИР2 (рис. 228) - сдвигающий регистр. Она имеет две одинаковые независимые секции по четыре разряда. Каждая секция имеет три входа - вход R для установки триггеров в нулевое

состояние, установка происходит при подаче лог. 1 на этот вход, вход С, по спадам импульсов отрицательной полярности на этом входе происходит запись информации со входа D в первый разряд регистра и сдвиг информации в сторону возрастания номеров. Для получения сдвигающего регистра с большим числом разрядов можно соединять входы D секций регистров с выходами 4 предыдущих разрядов и объединять одноименные входы С и R между собой.

Микросхема К176ИРЗ (рис. 228) - четырехразрядный сдвигаю-щий регистр. Запись информации со входа D0 и ее сдвиг происходят по спадам импульсов отрицательной полярности, подаваемых на вход С1 при лог. 0 на входе S. Параллельная запись информации со входов D1 - D4 происходит по спадам импульсов отрицательной полярности на входе С2 при лог. 1 на входе S. При объединении входов С1 и С2 выбор режима сдвига или записи производится по входу S. Если объединить входы С1 и S, специального сигнала управления не требуется.

Соединение входов D1 - D3 с выходами 2-4 превращает микросхему в реверсивный сдвигающий регистр.

Микросхема К561ИР6 - многофункциональный восьмиразрядный сдвигающий регистр (рис. 228). Микросхема имеет две группы информационных выводов - А1 - А8 и В1 - В8, каждая из которых может быть входами или выходами при параллельной записи и считывании, вход для последовательной записи информации D, входы управления P/S, A/S, А/В, ЕА, вход для подачи тактовых импульсов С. Сигналами на входах P/S, A/S, А/В, ЕА производится выбор режима работы микросхемы. Вход P/S (параллельный/последовательный) является преобладающим. При лог. 0 на этом входе независимо, от состояния других входов регистр переходит в режим последовательной записи информации со входа D по спадам импульсов отрицательной полярности на входе С и сдвига ее вправо (вниз по рис. 228). При лог. 1 на входе P/S регистр переходит в режим параллельной записи. Запись производится или по спадам импульсов отрицательной полярности на входе С (синхронная запись), при этом на входе A/S (асинхронно/синхронно) должен быть лог. 0, или по импульсам положительной полярности на входе A/S (асинхронная запись), при этом на входе С должны быть лог. 0 или лог. 1, но сигнал должен быть фиксированным. Какая из групп входов А или В при этом является входом, а какая - выходом, определяется сигналом на входе А/В -

если на этом входе лог. 1, входами являются выводы А1 - А8, выходами В1 - В8, при лог. 0 на входе А/В входы - В1 - В8, выходы А1 -А8. Независимо от сигнала на входе А/В лог. 0 на входе ЕА отключает группу выводов А от триггеров регистра. Если при этом на входе А/В лог. 0, возможна параллельная запись по группе В, но невозможно считывание по группе А, если на входе А/В лог. 1 - производится считывание по В, но невозможна запись по группе А, и при изменении сигналов на входах A/S и С состояние триггеров регистра не изменяется.

Выбор выходов при последовательной записи информации со входа D производится также сигналами на входах А/В и ЕА - при лог. 1 на входе А/В и произвольном сигнале на входе ЕА выходами является группа В, при лог. 0 на входе А/В и лог. 1 на входе ЕА выходы - группа А, при лог. 0 на входах А/В и ЕА обе группы А и В находятся в высокоимпедансном состоянии, считывание из регистра невозможно.

При включении нескольких микросхем К561ИР6 для увеличения числа разрядов одноименные управляющие входы и входы С микросхем следует объединить. При необходимости работы нескольких микросхем в режиме сдвига входы D последующих микросхем нужно подключить к выходам А8 или В8 предыдущих, при этом во время сдвига необходимо соответствующие группы выводов обязательно переводить в режим выхода, при использовании одиночной микросхемы этого не требуется.

Микросхема К561ИР6 может широко использоваться в аппаратуре в самых различных вариантах - от простейшего однонаправленного буфера до узла запоминания и коммутации данных, приходящих в последовательном или параллельном коде с двух направлений. Некоторые примеры использования этой микросхемы приведены в табл. 8, в ней указаны режим применения, входы и сигналы, которые надо зафиксировать для обеспечения этого режима, направление передачи сигнала и сигналы, подаваемые на используемые входы управления микросхемы. Знак <<Х>>указывает на то, что на данный вход может быть подан произвольный сигнал, знак «П» - на подачу импульса положительной полярности, знак «1» - срабатывание по спаду импуль-са отрицательной полярности. Знак <Z> означает высокоимпедансное состояние выхода.

Микросхема К561ИР9 - четырехразрядный сдвигающий регистр (рис. 228). Она имеет четыре выхода и следующие входы: вход сброса R,

вход для подачи тактовых импульсов С, вход выбора режима S, вход выбора полярности сигнала Р, входы для подачи информации при последовательной записи J и К и входы подачи информации при параллельной записи Dl, D2, D3, D4.

Вход R является преобладающим - при подаче на него лог. 1 независимо от состояния других входов все триггеры микросхемы устанавливаются в 0. Если на входе R лог. О, возможна запись информации в триггеры микросхемы. При лог. 1 на входе выбора режима S по спаду импульса отрицательной полярности на входе С произойдет параллельная запись информации в триггеры регистра со входов Dl - D4. Если на входе S лог. О, по спаду импульса отрицательной полярности на входе С произойдет запись информации со входов J и К в триггер с выходом 1 и сдвиг информации в остальных триггерах в сторону возрастания номеров выходов. Информация, которая будет записана в первый триггер, определяется состоянием входов J и К перед подачей спада импульса отрицательной полярности на вход С. Если объединить между собой входы J и К, будет производиться запись информации, имеющейся на этих объединенных входах. Если на вxoд J подать лог. 0, на вход К - лог. 1, изменения информации в первом триггере по спаду импульса отрицательной полярности на входе С не произойдет. При лог. 1 на входе J и лог. 0 на входе К первый триггер микросхемы переходит в счетный режим и меняет свое состояние на противоположное на каждый спад импульса отрицательной полярности на входе С.

Полярностью сигналов на выходах 1-4 регистра можно управлять подачей управляющего сигнала на вход Р - при лог. 1 на этом входе выходные сигналы выдаются в прямом коде, при лог. 0 - инвертируются.

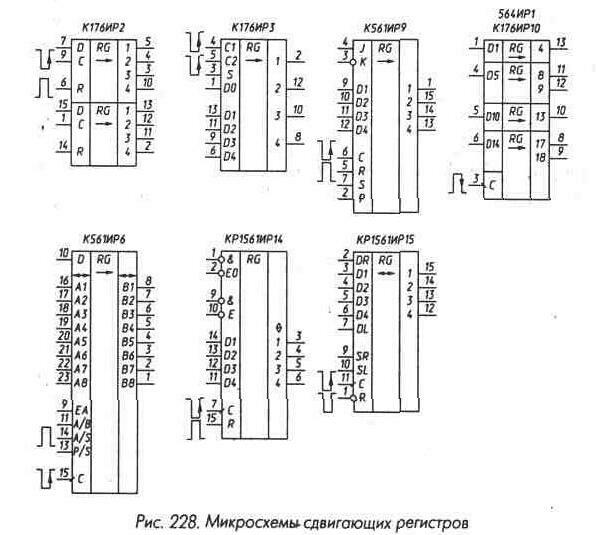

Для построения сдвигающего регистра с числом разрядов более четырех достаточно соединить выходы 4 микросхем младших разрядов с объединенными входами J и К микросхем следующих разрядов (рис. 229). Входы С, R, S различных микросхем следует соединить между собой, а на входы Р подать лог. 1.

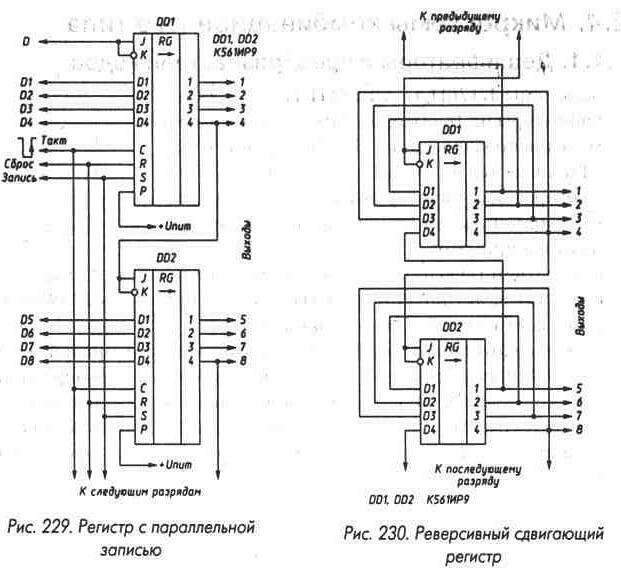

Для построения реверсивного сдвигающего регистра информационные входы микросхем J, К, Dl - D4 следует соединить с выходами в соответствии с рис. 230, входы С, R, S, Р - в соответствии с рис. 229. При лог. 0 на объединенных входах S будет происходить сдвиг информации в сторону возрастания номеров выходов (сверху вниз по схеме рис. 230), при лог. 1 - в сторону уменьшения (снизу вверх). Параллельная запись информации в такой регистр невозможна.

| Режим работы микросхемы К561ИР6 |

Фиксированные сигналы | Управляющие сигналы | Направление передачи сигналов, состояние выходов |

| Однонаправленный буфер | ЕА=1, А/В=1. A/S=1, P/S=1, С=Х | ----- | А--B |

| ЕА=1, А/В=0, A/S=1, P/S=1, С=Х | ------- | В--A | |

| Однонаправленный буфер с переводом выходов в высокоимпедансное состояние | A/S=1,P/S=1,C=X | ЕА=А/В=1 | А--В |

| ЕА=А/В=0 | A=B=Z | ||

| А/В=0, A/S=1, P/S=1, С=Х | ЕА=1 | В--А | |

| ЕА=0 | A=B=Z | ||

| Двухнаправленный буфер | A/S=1,P/S=1,C=X | ЕА=А/В=1 | А---В |

| ЕА=1.А/В=0 | В-А | ||

| ЕА=А/В=0 | A=B=Z - | ||

| Регистр хранения с асинхронной записью и с переводом выходов в высокоимпедансное состояние | P/S=1,C=X | ЕА=А/В=1.А/S=П | А--В |

| EA=A/B=A/S=0 | A=B=Z | ||

| A/B=0,P/S=1,C=X | ЕА=1,А/S=П | В->А | |

| EA=A/S=0 | A=B=Z | ||

| Регистр хранения с синхронной записью и с переводом выходов в высокоимпедансное состояние | A/S=0.P/S=1 | ЕА=А/В=1.С=I | А--В |

| ЕА=А/В=0. С=I | A=B=Z | ||

| A/B=0, A/S=0,P/S=1 | EA=1,C=I | В--А | |

| ЕА=0. С=Х | A=B=Z | ||

| Сдвигающий регистр с последовательной записью, параллельным считыванием | EA=1, A/B=0, A/S=X, P/S=0 | C=I | Выходы А |

| EA=X, A/B=1, A/S=X, P/S=0 | Выходы В | ||

| Регистр с асинхронной параллельной записью и последовательным считыванием | A/S=P/S= П, С=Х | Входы А | |

| EA=1,A/B=1 | A/S=P/S=0. C=I | Выход В8 | |

| EA=1,A/B=0 | A/S=P/S=П.C=X | Входы В | |

| A/S=P/S=0, C=T | Выход А8 | ||

| Регистр с синхронной параллельной записью и последовательным считыванием | EA=1,A/B=1,A/S=0 | P/S=1¦ P/S=0¦ C=I P/S=1¦ P/S=0¦ | Входы А |

| Выход В8 | |||

| EA=1,A/B=0,A/S=0 | Входы В | ||

| Выход А8 | |||

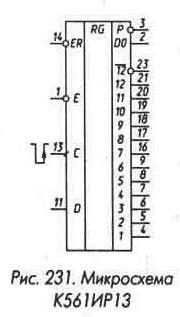

Микросхема 564ИР13 (рис. 231) - специальный регистр, предназначенный для построения аналого-цифровых преобразователей, работающих по принципу последовательного приближения, с числом разрядов до 12. Логика работы микросхемы полностью соответствует работе микросхемы К155ИР17 (см. рис. 60-63).

Микросхема КР1561ИР14 (рис. 228) - четырехразрядный регистр хранения информации с возможностью перевода выходов в высокоимпедансное состояние. Логика ее работы совпадает с работой микросхемы К155ИР15 (см. рис. 57,58).

Микросхема КР1561ИР15 (рис. 228) - универсальный четырехразрядный сдвигающий ре-

гистр, позволяющий производить как параллельную запись информации, так и ее сдвиг вправо и влево, она работает так же, как и К555ИР11 (см. рис. 50, 51).