1.3.2. Счетчики

В состав рассматриваемых серий ТТЛ-микросхем входит большое число счетчиков и делителей частоты, различающихся по своим свойствам и назначению.

Микросхема К155ИЕ1 (рис. 24) - делитель частоты на 10. Установка триггеров микросхемы в 0 осуществляется подачей лог. 1 одновременно на два объединенных по схеме И входа R. Рабочая полярность входных счетных импульсов, подаваемых на входы С, отрицательная. Импульсы можно подавать или отдельно на каждый из входов (на второй вход

должна при этом подаваться лог. 1), или одновременно на оба входа. Одновременно с каждым десятым входным импульсом на выходе формируется равный ему по длительности выходной импульс отрицательной полярности. Многокаскадные делители частоты можно строить, соединяя входы С последующих каскадов с выходами предыдущих.

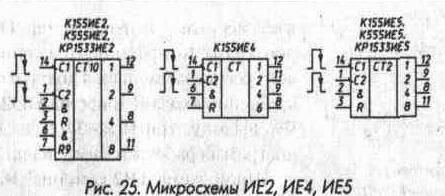

Микросхемы ИЕ2, К155ИЕ4 и ИЕ5 (рис. 25) содержат по четыре счетных триггера. В каждой микросхеме один из триггеров имеет отдельный вход С1 и прямой выход, три оставшихся триггера соединены между собой так, что образуют делитель на 8 в микросхеме ИЕ5,

на 6 в К155ИЕ4 и на 5 в ИЕ2. При соединении выхода первого триггера с входом С2 цепочки из трех триггеров образуются соответственно делители на 16, 12 и 10. Делители на 10 и 16 работают в коде 1-2-4-8, делитель на 12 - в коде 1-2-4-6. Микросхемы имеют по два входа R установки в 0, объединенные по схеме И. Сброс (установка в 0) триггеров производится при подаче лог. 1 на оба входа R. Микросхема ИЕ2 имеет, кроме того, входы R9 для установки в состояние 9, при котором первый и последний триггеры декады находятся в единичном состоянии, остальные - в нулевом.

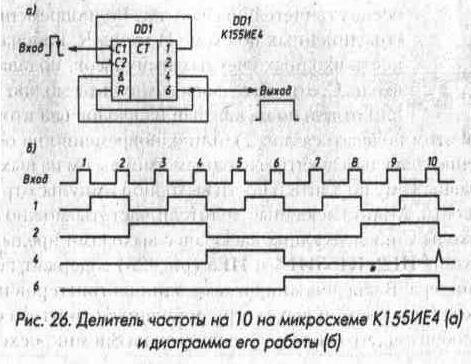

Наличие входов установки, объединенных по схеме И, позволяет строить делители частоты с различными коэффициентами деления в пределах 2-6 без использования дополнительных логических элементов. На рис. 26 приведены схема декады на микросхеме К155ИЕ4 и ее временная диаграмма. До прихода десятого импульса декада работает как делитель частоты на 12. Десятый импульс переводит триггеры микросхемы в состояние 10, при котором на выходах 4 и 6 микросхемы формируются уровни лог. 1. Эти уровни, поступая на входы

R микросхемы, переводят ее в 0, в результате чего коэффициент пересчета К становится равным 10

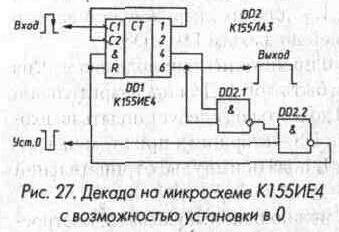

Для установки рассмотренной декады в 0 внешним сигналом необходимо введение в нее логических элементов И-НЕ (рис 27)

В табл. 4 приведены номера выводов микросхем, которые нужно соединить между собой для получения различных К Все делители, полученные соединением выводов по табл. 4, работают по одно

му принципу - при достижении состояния, соответствующего необходимому коэффициенту пересчета, происходит установка счетчика в 0. Исключение составляет делитель на 7 на микросхеме ИЕ2. В этом делителе после подсчета шести импульсов на входах R9 формируются уровни лог. 1, поэтому из состояния 5 делитель сразу переходит в состояние 9, минуя 6,7 и 8 Код работы этого делителя - невесовой

Делители на микросхемах ИЕ5 и ИЕ2 работают в весовом коде 1-2-4-8, на микросхеме К155ИЕ4 - в коде 1-2-4-6 при использовании входа 14 и в коде 1-2-3 - при использовании входа 1.

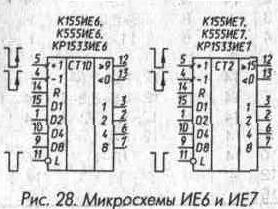

Микросхемы ИЕ6 и ИЕ7 - реверсивные счетчики. Первый из них - двоично-десятичный, второй - двоичный Оба работают в коде 1-2-4-8 Цоколевка обеих микросхем одинакова (рис 28), различие в том, что первый считает до 10, второй до 16

Рассмотрим для примера работу микросхемы ИЕ6 В отличие от рассмотренных ранее счетчиков, эта микросхема имеет большее число

Таблица 4

| К | К155ИЕ2 |

К155ИЕ4 | К155ИЕ5 | ||||||

| Вход | Вых. | Соединить выводы | Вход | Вых. | Соединить выводы | Вход | Вых. | Соединить выводы | |

| 2 | 14 | 12 | 14 | 12 | - | 14 | 12 | - | |

| 3 | 1 | 8 | 9-2,8-3 | 1 | 9 | - | 1 | 8 | 9-2,8-3 |

| 4 | 1 | 8 | 11-2-3 |

1 | 8 | 11-6,8-7 | 1 | 8 | - |

| 5 | 1 | 11 | - | 1 | 8 | 9-6,8-7 | 1 | 11 | 9-2,11-3 |

| 6 | 14 | 8 | 12-1,9-2,8-3 | 1 | 8 | - | 1 | 11 | 8-2,11-3 |

| 7 | 14 | 11 | 12-1,9-6,8-7 | 14 | 8 | 12-1-6,8-7 | - | - | - |

| 8 | 14 | 8 | 12-1,11-2-3 | 14 | 8 | 12-1,11-6,8-7 | 1 | 11 | - |

| 9 | 14 | 11 | 12-1-2,11-3 | - | - | - | 14 | 11 | 12-1-2,11-3 |

| 10 | 14 | 11 | 12-1 | 14 | 8 | 12-1,9-6,8-7 | 14 | 11 | 12-1,9-2,11-3 |

| 12 | - | 14 | 8 | 12-1 | 14 | 11 | 12-1,8-2,11-3 | ||

| 16 | - | - | - | - | - | - | 14 | 11 | 12-1 |

выходов и входов Входы +1 и -1 служат для подачи тактовых импульсов, +1 - при прямом счете, -1 - при обратном. Вход R служит для установки счетчика в 0, вход L - для предварительной записи в счетчик информации, поступающей по входам D1 - D8.

Установка триггеров счетчика в 0 происходит при подаче лог 1 на вход R, при этом на входе L должна быть лог. 1. Для предварительной записи в счетчик любого числа от 0 до 9 его код следует подать на входы D1 - D8 (D1 - младший разряд, D8 - старший), при этом на входе R должен быть лог 0, и на вход L подать импульс отрицательной полярности

Режим предварительной записи можно использовать для построения делителей частоты с перестраиваемым коэффициентом деления для учета фиксированной частоты (например, 465 кГц) в цифровой шкале радиоприемника Если этот режим не используется, на выходе L должен постоянно поддерживаться уровень лог 1

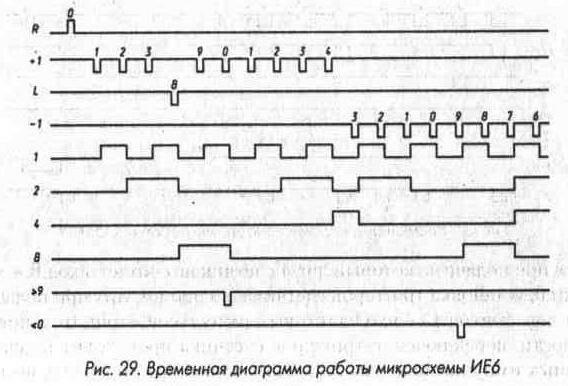

Прямой счет осуществляется при подаче импульсов отрицательной полярности на вход +1, при этом на входах -1 и L должна быть лог 1, на входе R - лог 0 Переключение триггеров счетчика происходит по спадам входных импульсов, одновременно с каждым десятым входным импульсом на выходе >=9 формируется отрицательный выходной импульс переполнения, который может подаваться на вход +1 следующей микросхемы многоразрядного счетчика Уровни на выходах 1-2-4-8 счетчика соответствуют состоянию счетчика в данный момент (в двоичном коде) При обратном счете входные импульсы подаются на вход -1, выходные импульсы снимаются с выхода <=0 Пример временной диаграммы работы счетчика приведен на рис. 29.

Первый импульс установки в 0 устанавливает все триггеры счетчика в 0. Три следующих импульса, поступающих на вход +1, переводят счетчик в состояние 3, которому соответствуют лог. 1 на выходах 1 и 2 и лог 0 - на 4 и 8. Если на входах D1 - D4 лог. 0, на входе D8 лог. 1, импульс на входе L устанавливает счетчик в состояние 8 Следующие

шесть импульсов, поступающие на вход +1, переводят счетчик последовательно в состояния 9,0,1,2,3,4 Одновременно с импульсом, переводящим счетчик в 0, на выходе S9 появляется выходной импульс прямого счета Следующие импульсы, поступающие на вход -1, изменяют состояние счетчика в обратном порядке 3, 2, 1,0,9,8 и т д

Одновременно с импульсом обратного счета, переводящим счетчик в состояние 9, на выходе <=0 появляется выходной импульс.

В микросхеме ИЕ7 импульс на выходе =>15 появляется одновременно с импульсом на входе +1 при переходе счетчика из состояния 15 в состояние 0, а на выходе <=0 - при переходе счетчика из 0 в 15 одновременно с импульсом на входе -1.

Предельная частота функционирования микросхем К155ИЕ6, К155ИЕ7 - 15 МГц, К555ИЕ6 и К555ИЕ7 - 25 МГц, КР1533ИЕ6 и КР1533ИЕ7 - 30 МГц.

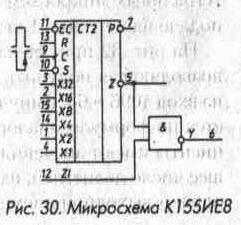

Микросхему К155ИЕ8 обычно называют делителем частоты с переменным коэффициентом деления, однако это не совсем точно. Эта микросхема содержит шестиразрядный двоичный счетчик, элементы совпадения, позволяющие выделять не совпадающие между собой импульсы - каждый второй, каждый четвертый, каждый восьмой и т. д. и управляемый элемент И-ИЛИ, который позволяет подавать на выход часть или все выделенные импульсы, в результате чего сред-

няя частота выходных импульсов может изменяться от 1/64 до 63/64 частоты входных импульсов. Графическое обозначение микросхемы приведено на рис. 30, пример временной диаграммы ее работы - на рис. 31. Для наглядности на рис. 30 вынесен логический элемент И-НЕ, входящий в микросхему. Микросхема имеет следующие входы: инверсный вход ЕС - разрешения

счета, при подаче на который лог. 1 счетчик не считает, вход R - установки 0, установка триггеров счетчика в 0 происходит при подаче на него лог. 1; вход С - вход тактовых импульсов отрицательной полярности, переключение триггеров счетчика происходит по спадам входных импульсов; входы XI - Х32 позволяют управлять выдачей отрицательных выходных импульсов, совпадающих по времени с входными, на выход Z. На рис. 31 в качестве примера показано, какие импульсы выделяются на выходе Z при подаче лог. 1 на входы:

Х32 (диаграмма Х32), Х16 (диаграмма Х16) и Х8 (диаграмма Х8). В этих случаях на выходе Z выделяется соответственно 32, 16 или 8 равномерно расположенных импульсов. Если же одновременно подать лог. 1 на несколько входов, например, на Х32 и Х8, то, как показано на диаграмме Z, на выходе Z выделится 40 импульсов, но расположенных неравномерно. В общем случае число импульсов N на выходе Z за период счета составит

N = 32 х Х32 + 16 х Х16 + 8 х Х8 + 4 х Х4 + 2 х Х2 + X1, где X1-Х32 принимают значения соответственно 1 или 0 в зависимости от того, подана или нет лог. 1 на соответствующий вход.

На выходе Р выделяется отрицательный импульс, фронт которого совпадает со спадом 63-го тактового импульса, спад - со спадом 64-го. Этот импульс может использоваться при каскадном соединении интегральных микросхем К155ИЕ8. Вход S - вход стробирования, при подаче на него лог. 1 выдача импульсов на выходе Z прекращается.

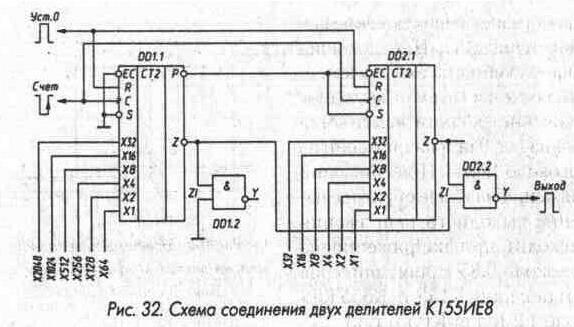

На рис. 32 приведена схема соединения двух делителей К155ИЕ8, позволяющая получить на выходе от 1 до 4095 импульсов при подаче на вход 4096 =64^2 импульсов. Число импульсов на выходе подсчитывается по формуле, аналогичной приведенной выше, в которой коэффициенты имеют значения от 2048 до 1. Если требуется соединить большее число делителей, их соединение производится аналогично рис. 32, однако выходной элемент И-НЕ, выполняющий функцию ИЛИ-НЕ

для отрицательных импульсов, поступающих с выходов Z делителей, необходимо использовать из отдельной микросхемы И-НЕ или И.

Микросхема ИЕ9 (рис. 33) - синхронный десятичный счетчик с возможностью параллельной записи информации по фронту тактового импульса, имеет девять входов. Подача лог. 0 на вход R независимо от состояния других входов приводит к установке триггеров микросхемы в состояние 0. Для обеспечения режима счета на входе R необходимо подать лог. 1, тот же сигнал должен быть подан на входы разрешения параллельной записи EL, разрешения ЕС, разрешения выдачи сигнала переноса ER Изменение состояния триггеров счетчика при счете происходит по спаду импульсов отрицательной полярности, подаваемых на вход С.

При подаче лог. 0 на вход EL микросхема переходит в режим параллельной записи информации со входов D1 - D8. Запись происходит по спадам импульсов отрицательной полярности на входе С, что позволяет использовать микросхему в режиме сдвигающего регистра. При записи на входе R должна быть лог. 1, сигналы на входах ЕС и ЕР произвольны.

На выходе переноса Р лог. 1 появляется в том случае, когда счетчик находится в состоянии 9, а на входе ЕР - лог. 1, в остальных случаях на выходе Р лог. 0. Подача лог. 0 на вход ЕР запрещает выдачу лог. 1 на выходе Р и счет импульсов. Подача лог. 0 на вход ЕС запрещает счет, но не запрещает выдачу сигнала переноса. Сигнал запрета счета (лог. 0 на входах ЕС и ЕР) действует лишь в том случае, если он полностью перекрывает по длительности импульс отрицательной полярности на входе С, в том числе он может совпадать с ним по времени.

Для обеспечения параллельной записи лог. 0 на вход EL информация на входы D1 - D8 может быть подана как при лог. 1, так и при лог. 0 на входе С и удерживаться до момента перехода лог. 0 на входе С в лог. 1, когда и произойдет запись.

Для обеспечения счета с числа, введенного в микросхему при параллельной записи, лог 0 на входе EL должен быть изменен на лог. 1 или одновременно с переходом лог. 0 в лог. 1 на входе С, или при лог. 1 на входе С.

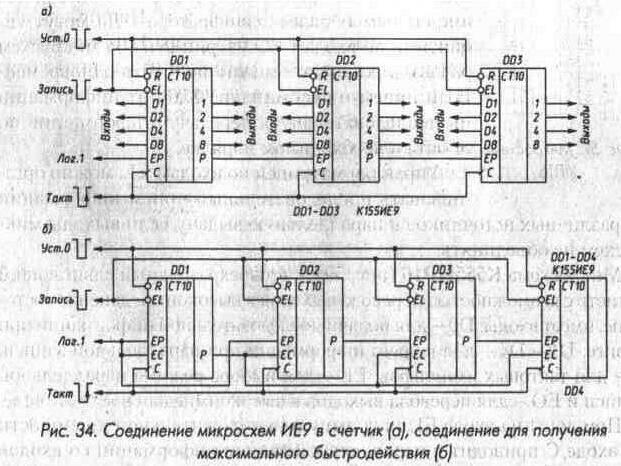

На рис. 34 (а) приведена схема соединения микросхем ИЕ9 в многоразрядный синхронный счетчик, которая снижает быстродействие счетчика, так как для его нормальной работы необходимо, чтобы сигнал переноса от младшего разряда прошел через все микросхемы до старшего разряда до подачи очередного тактового импульса. Для получения максимального быстродействия многоразрядного счетчика, равного быстродействию отдельной микросхемы, микросхемы можно соединить по схеме рис. 34 (б). В этом случае сигнал переноса с выхода Р микросхемы DD1 разрешает работу остальных микросхем, соединенных в счетчик по схеме рис. 34 (а), лишь в те моменты, когда микросхема DD1 находится в состоянии 9, поэтому от счетчика DD2 - DD9 требуется быстродействие в 10 раз меньшее быстродействия микросхемы DD1, что обеспечивается при любой практически встречающейся длине счетчика.

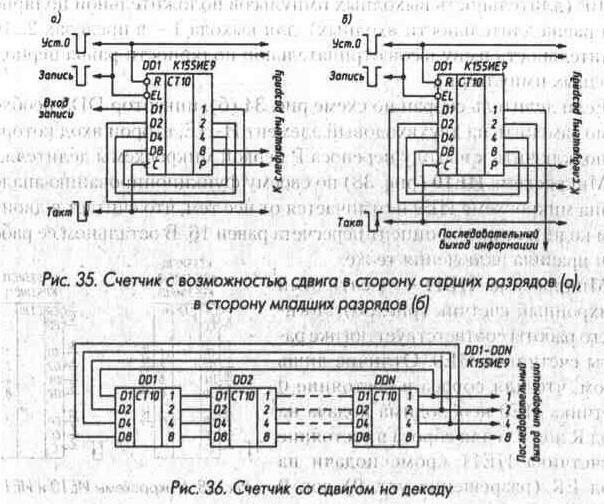

Как уже указывалось выше, микросхемы ИЕ9 могут работать в режиме сдвигающего регистра. Для обеспечения такого режима необходимо входы D1 - D8 соединить с выходами 1-2-4-8 в нужном порядке. Для сдвига информации на один двоичный разряд по каждому тактовому импульсу в сторону старших разрядов соединение необходимо произвести в соответствии с рис. 35 (а). Для обеспечения динамической индикации удобно сдвигать информацию сразу на один десятичный разряд, а сдвигающий регистр замыкать в кольцо. Такая возможность проиллюстрирована на рис. 36.

На рис. 36 не показаны цепи подачи импульсов и управляющих сигналов, которые могут быть выполнены в соответствии с рис. 34 (а) или 34 (б). Роль входа разрешения сдвига выполняет вход Запись. Естественно, что при соединении микросхем в соответствии с рис. 35,36 параллельная запись информации в микросхемы невозможна.

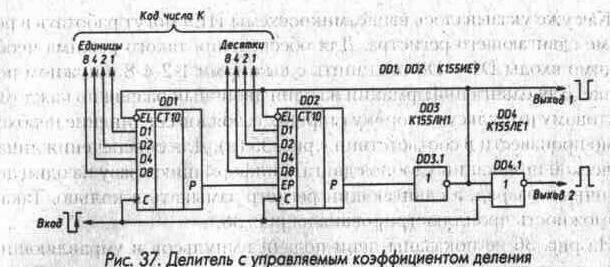

Микросхемы ИЕ9 удобно использовать в делителе с переключаемым коэффициентом пересчета. Для получения указанного режима достаточно сигнал переноса старшего разряда одноразрядного или многоразрядного счетчика через инвертор подать на вход разрешения записи, а на входы D1 - D8 подать код, определяющий коэффициент пересчета (рис. 37).

При установке счетчика в процессе счета в состояние 99...9 счетчик перейдет в режим параллельной записи и при подаче следующего тактового импульса вместо перехода в состояние 00...0 произойдет запись параллельного кода, поданного на входы D1 - D8 микросхем. В результате общий коэффициент пересчета N уменьшится на величину К, соответствующую численному значению этого кода, и составит

![]()

Коэффициент пересчета может меняться для выхода 2 в пределах 1...10^м (длительность выходных импульсов положительной полярности равна длительности входных), для выхода 1 - в пределах 2...10^м (длительность импульсов отрицательной полярности равна периоду входных импульсов).

Если делитель собран по схеме рис. 34 (б), инвертор DD3 необходимо заменить на двухвходовый элемент И-НЕ, второй вход которого подключить к выходу переноса Р первой микросхемы делителя.

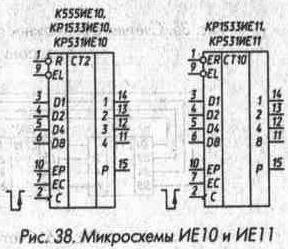

Микросхема ИЕ10 (рис. 38) по своему функционированию аналогична микросхеме ИЕ9 и отличается от нее тем, что считает в двоичном коде, и ее коэффициент пересчета равен 16. В остальном ее рабо

та и правила включения те же.

Микросхема ИЕ11 - десятичный синхронный счетчик (рис. 38). Логика его работы соответствует логике работы счетчиков ИЕ9. Отличие лишь в том, что для сброса в состояние 0 счетчика ИЕ9 необходима подача на вход R лог. 0, а для сброса в состояние 0 счетчика ИЕ11 кроме подачи на вход ER (разрешение уст. 0) лог. 0

необходима подача тактового импульса отрицательной полярности на вход С, по спаду которого и происходит сброс счетчика. Таким образом, все изменения выходных сигналов этой микросхемы происходят по спаду импульсов отрицательной полярности на входе С.

Микросхема КР1533ИЕ12 (рис. 39) обеспечивает параллельную запись и режим счета. Входы Dl, D2, D4, D8 служат для подачи сигналов кода при параллельной записи информации. Запись в триггеры счетчика происходит асинхронно при поступлении на вход L лог. 0 независимо от состояния других входов. При лог. 1 на входе L и лог. 0 на входе разрешения работы Е счетчик изменяет состояние по спадам импульсов отрицательной полярности на входе С. На

правление счета определяется сигналом на входе D/U: при лог. 0 происходит счет вверх, при лог. 1 - вниз.

Для построения многоразрядных счетчиков у микросхемы есть два специальных выхода: последнего состояния 0/9 и переноса Р. На выходе 0/9 лог. 1 появляется при достижении состояния 9 при прямом счете и состояния 0 при обратном. В остальных случаях на выходе 0/9 - лог. 0. При наличии лог. 1 на выходе 0/9 и лог. 0 на входе Е одновременно с импульсом на входе С на выходе переноса Р появляется импульс отрицательной полярности и той же длительности.

Счетчик КР1533ИЕ12 не имеет входа установки в 0. Для этой цели на входы Dl, D2, D4, D8 подают лог. 0, а на вход L - импульс отрицательной полярности. Смена сигналов на входах D/U и Е должна происходить в момент переключения сигнала на входе С из лог. 0 в лог. 1 или в паузе между импульсами на входе С (то есть при лог. 1 на этом входе).

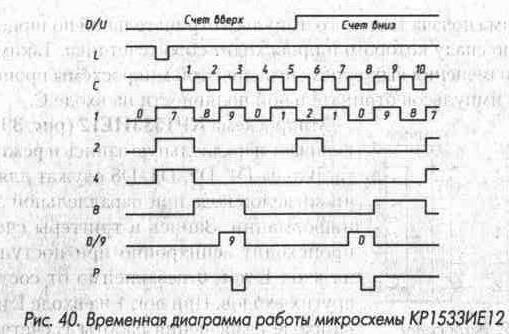

Пример временной диаграммы работы счетчика представлен на рис. 40. По импульсу отрицательной полярности на входе L записываются сигналы кода числа 7 в триггеры счетчика (сигналы кода 0111 на входах D8, D4, D2, Dl не показаны). Первые пять импульсов на входе С переводят его последовательно в состояния 8, 9, 0, 1, 2. На выходе 0/9 лог. 1 появляется при переходе счетчика в состояние 9. Импульс на его выходе Р формируется одновременно с третьим импульсом на входе С, по спаду которого счетчик переключается в состояние 0.

В момент окончания пятого импульса происходит смена направления счета изменением сигнала на входе D/U и следующие пять импульсов на входе С переводят счетчик последовательно в состояния 1, 0, 9,

8,7 и т. д. При переходе счетчика в состояние 0 на выходе 0/9 появляется лог. 1, а одновременно с восьмым импульсом на входе С, переключающим счетчик в состояние 9, на выходе Р формируется импульс отрицательной полярности.

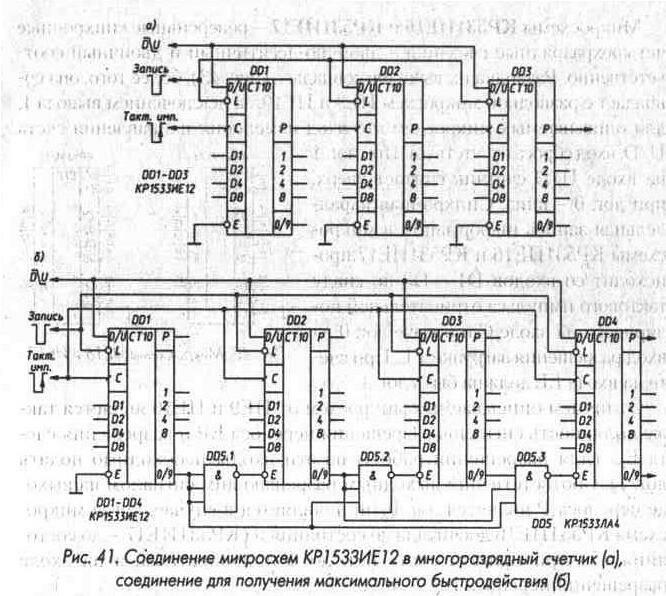

Схема соединения микросхем КР1533ИЕ12 в многоразрядный счетчик показана на рис. 41 (а). Из-за последовательного переключения быстродействие такого счетчика в реверсивном режиме снижается относительно быстродействия одной микросхемы.

Если необходим реверсивный счетчик с максимально возможным быстродействием, его собирают по схеме рис. 41 (б). В этом счетчике все триггеры микросхем переключаются одновременно и его быстродействие не зависит от числа разрядов. Однако для каждого десятичного разряда, кроме первого, требуется элемент И-НЕ с числом входов, возрастающим по мере роста номера разряда.

В зависимости от необходимого быстродействия возможно построение различных вариантов последовательно-параллельного счетчика. Можно, например, не использовать выход 0/9 микросхемы DD4 (рис. 41, б), а ее выход Р соединить с входом тактовых импульсов второго такого счетчика.

Микросхема КР1533ИЕ13 (рис. 39) аналогична КР1533ИЕ12, но ее коэффициент пересчета равен 16. Все правила ее использования и схемы включения соответствуют микросхеме КР1533ИЕ12.

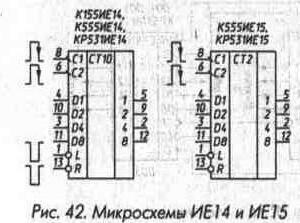

Микросхема ИЕ14 (рис. 42) во многом напоминает микросхему ИЕ2. Она также содержит счетный триггер с входом С2. При соединении выхода 1 счетного триггера (вывод 5) с входом С2 образуется двоично-десятичный счетчик, работающий в коде 1-2-4-8. Срабатывание триггера и делителя на 5 происходит по спадам импульсов положительной

полярности. Различие с микросхемой ИЕ2 заключается в полярности импульсов сброса - триггеры микросхемы ИЕ14 устанавливаются в 0 при подаче на вход R лог. 0. Кроме того, в микросхеме ИЕ14 есть возможность предварительной установки триггеров счетчика. Для установки триггеров необходимый код следует подать на входы D1 - D8, а на вход L - импульс отрицательной полярности. При лог. 0 на входе L сигналы на выходах 1-8 повторяют сигналы на входах D1 - D8, при лог. 1 происходит запоминание и возможен счетный режим работы микросхемы.

Микросхему можно использовать в счетчиках с предварительной установкой, например, в цифровых шкалах радиоприемников и трансиверов с учетом промежуточной частоты.

Микросхема ИЕ15 (рис. 42) по своей структуре и функционированию аналогична микросхеме ИЕ14, но делитель с входом С2 делит частоту на 8,

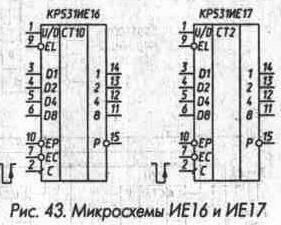

Микросхемы КР531ИЕ16 и КР531ИЕ17 - реверсивные синхронные четырехразрядные счетчики - двоично-десятичный и двоичный соответственно. Разводка их выходов совпадает (рис. 43), более того, она совпадает с разводкой микросхем ИЕ9 и ИЕ10, за исключением вывода 1, для описываемых микросхем это вход изменения направления счета

U/D, вход сброса отсутствует. При лог. 1 на входе U/D счетчик считает вверх, при лог. 0 - вниз. Синхронная параллельная запись информации в микросхемы КР531ИЕ16 и КР531ИЕ17 происходит со входов D1 - D8 по спаду тактового импульса отрицательной полярности на входе С и подаче лог. 0 на вход разрешения загрузки EL. При счете на входе EL должна быть лог. 1.

Отличием описываемых микросхем от ИЕ9 и ИЕ10 является также полярность сигналов разрешения переноса ЕР и разрешения счета ЕС (для разрешения работы на эти входы необходимо подать лог. 1). Соответственно выходным разрешающим сигналом на выходе переноса Р является лог. 0, он появляется в случае, когда микросхема КР531ИЕ16 досчитала до состояния 9 (КР531ИЕ17 - до состояния 15) при прямом счете или до 0 при обратном, а на входе разрешения переноса ЕР - лог. 0.

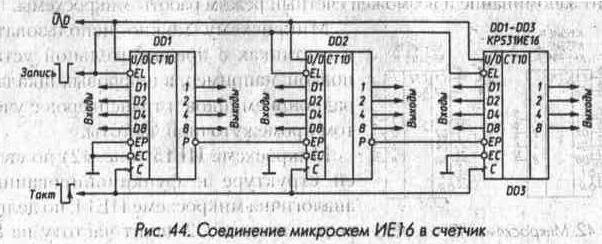

Примеры соединения микросхем КР531ИЕ16 и КР531ИЕ17 в многоразрядный счетчик приведены на рис. 44 и 45. При соединении микросхем по схеме рис. 44 максимальная частота счета снижается по отношению к максимально возможной для одной микросхемы, при соединении по схеме рис. 45 - не снижается. Следует помнить, что переключение направления счета на входе U/D и смену информации на входах ЕР и ЕС следует производить в паузе между

тактовыми импульсами, то есть при лог. 1 на входах С микросхем или в момент изменения сигнала на этих входах с лог. 0 на лог. 1. Входной ток микросхем по входу ЕР в состоянии лог. 0-4 мА. Микросхема ИЕ18 (рис. 46) аналогична по функционированию микросхеме ИЕ11, но ее коэффициент пересчета равен 16.

Рассмотренные выше микросхемы счетчиков серии КР531 имеют входные токи по управляющим входам, как правило, больше стандартных. При подаче на входы лог. 0 токи составляют для микросхем КР531ИЕ9 и КР531ИЕ10 по выводу 2 - 5 мА, выводу 10-3 мА, выводу 9-4 мА. Для микросхем КР531ИЕ11 и КР531ИЕ18 ток по вы

воду 10 составляет 4 мА, а для КР531ИЕ14 и КР531ИЕ15 ток по выводу 8-8 мА, по выводу 6-10 мА, по выводам 1, 3, 4, 10, 11, 13 - 0,75 мА.

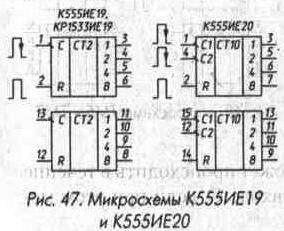

Микросхема К555ИЕ19 - два четырехразрядных двоичных счетчика (рис. 47), каждый из которых имеет два входа: R - для установки триггеров счетчика в 0 при подаче на вход R лог. 1 и С - для подачи счетных импульсов. Срабатывание триггеров счетчика происходит по спадам импульсов положительной полярности, подаваемых на вход С,

выходной код счетчиков - стандартный, 1-2-4-8. Для соединения счетчиков в многоразрядный выходы 8 предыдущих разрядов необходимо соединить со входами С последующих.

Микросхема К555ИЕ20 (рис. 47) -два четырехразрядных двоично-десятичных счетчика, каждый из которых аналогичен счетчику микросхем ИЕ2, за исключением входов установки в 0 R.

Каждый счетчик имеет триггер со входом С1, выходом 1 и делитель частоты на 5 со входом С2 и выходами 2,4,8. Триггер и счетчик срабатывают по спадам положительных импульсов, подаваемых на входы С1 и С2, на входе R при счете должен быть лог. 0. Для получения десятичного счетчика выход 1 надо соединить со входом С2, при этом код счетчика будет 1-2-4-8. Если же выход 8 соединить со входом С1, входные импульсы подать на вход С2, выходной код будет 1-2-4-5, а на выходе 1 сигнал будет иметь форму меандра с частотой, в 10 раз меньше входной. Впрочем, так же можно соединять счетчики микросхем ИЕ2 и ИЕ14. Предельная частота работы триггера - 25 МГц, делителя на 5 - 20 МГц.