1.8. Деление частоты

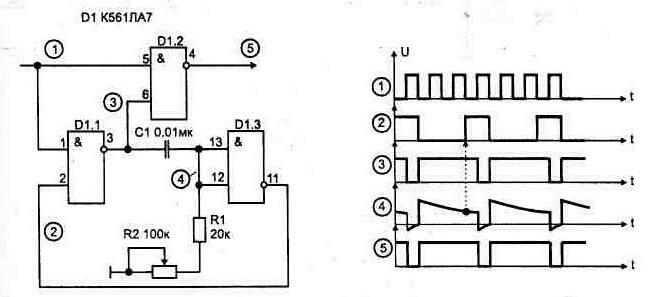

Наиболее часто для этого используют счетчики, хотя можно разделить частоту с помощью ждущего мультивибратора, ограничив число проходящих на выход импульсов. Пример такой схемы показан на рис. 1.60. Как только импульс входной частоты поступает на выход 5, ждущий мультивибратор D1.1, D1.3 запирает элемент D1.2 на время, определяемое резистором R1. Когда ждущий мультивибратор возвращается в исходное состояние, на выход поступает следующий импульс и цикл возобновляется. Схему можно усовершенствовать, заменив потенциометр полевым транзистором, что позволит управлять коэффициентом деления с помощью напряжения.

Рис. 1.60 Делитель частоты с использованием ждущего мультивибратора

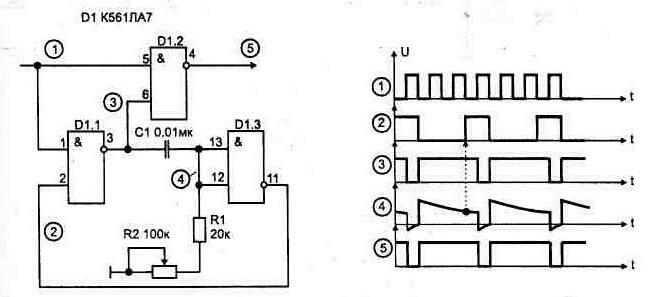

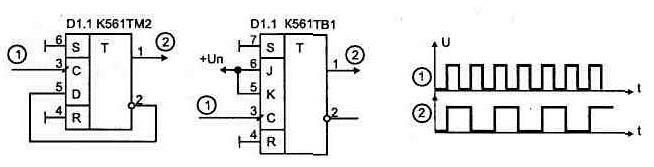

Делитель на 2 можно собрать из простейших ЛЭ, рис. 1.61. Схемы делителей без использования RC-цепей имеют лучшую помехоустойчивость и болееширокий диапазон входной частоты сигнала. Основным элементом всех счетчиков является триггер с так называемым счетным входом, рис. 1.62. Таблица 1.4

Рис. 1.61. Счетный триггер на логических элементах

Таблица 1.4

| Сигналы на входах | Состояние выхода | ||||

| С | D | S | R | Q | NOT Q |

| х | х | 0 | 1 | 0 | 1 |

| х | х | 1 | 0 | 1 | 0 |

| _/ | 0 | 0 | 0 | 0 | 1 |

| _/ | 1 | 0 | 0 | 1 | 0 |

| \_ | х | 0 | 0 | Q | NOT Q |

Рис. 1.62. Делитель частоты на 2

Рис. 1.63. Делитель на 3

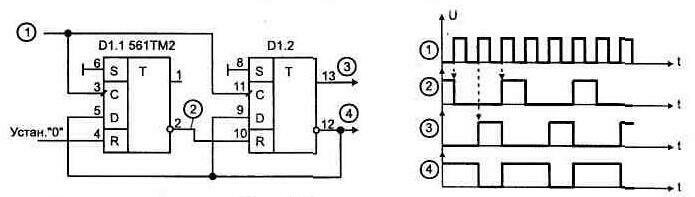

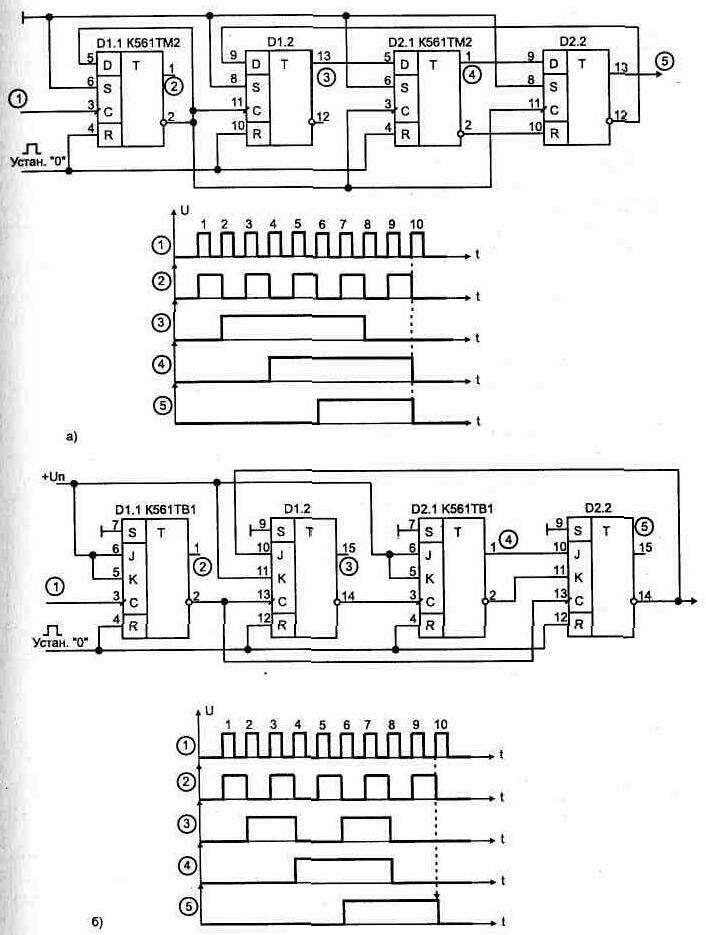

Рис. 1.64. а) Делитель на 10 на RS-триггерах; б) делитель на 10 на JK-триггерах

поясняет логику работы триггера 561ТМ2 в зависимости от управляющих сигналов (х — безразлично состояние на данном входе; состояние, когда на входах S и R микросхемы одновременно действует лог. "1", является запрещенным).

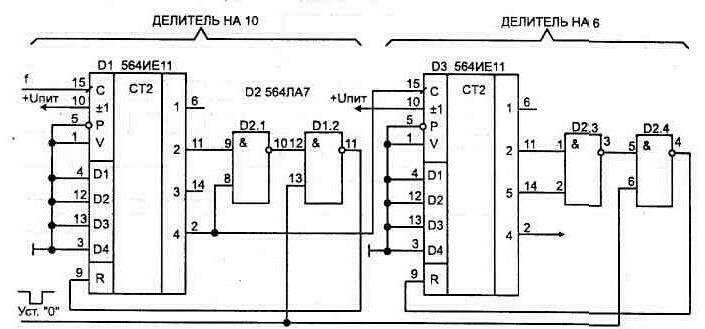

Комбинационное включение триггеров позволяет получать счетчик с нужным коэффициентом деления входной частоты. На рис. 1.63...1.65 приведены примеры включения элементов микросхем для получения деления на 2, 3, 6, 10 и 60.

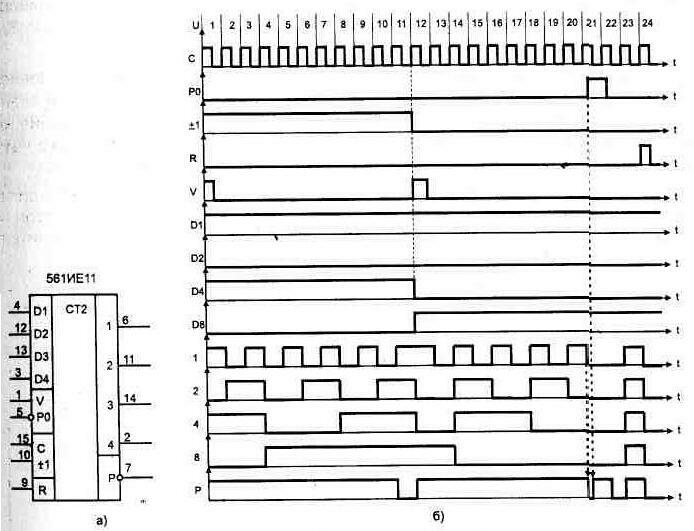

Промышленность выпускает универсальные счетчики, которые в зависимости от управляющих сигналов могут переключаться по переднему или заднему фронту входного сигнала, а также менять направление счета (сложение или вычитание). В качестве примера приведена диаграмма работы двоичного четырехразрядного реверсивного счетчика на микросхеме 561ИЕ11, рис. 1.66.

Таблица истинности (табл. 1.5) поясняет назначение управляющих сигналов и логику управления микросхемой (1 — лог. "1"; 0 — лог. "0"; х — состояние безразлично, т. е. 0 или 1). Счетчик предусматривает возможность загрузить по входам D1, D2, D4, D8 параллельный код.

Рис. 1 65. Схема делителя на 60

Таблица 1.5

| Вход переноса РО |

Сложение, вычитание +-1 |

Разрешен. установки V |

Установка нуля R |

Действие |

| 1 | х | 0 | 0 | нет счета |

| 0 | 1 | 0 | 0 | работа на сложение |

| 0 | 0 | 0 | 0 | работа на вычитание |

| х | х | 1 | 0 | установка по парал. вх. |

| х | х | х | 1 | установка нуля |

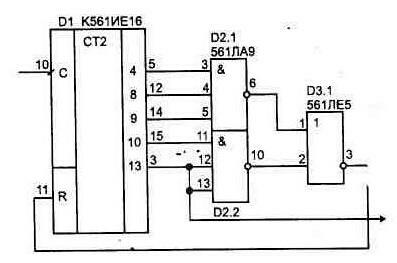

Для получения нужного

коэффициента деления можно использовать

микросхемы двоичных счетчиков, соединяя

соответствующие выходы с помощью ЛЭ, рис. 1.67, или

же применить счетчик с программируемым

коэффициентом деления 564ИЕ15, см. рис. 1.26.

Рис. 1. 66. а)

Универсальный реверсивный счетчик,

б) диаграмма напряжении микросхемы

Pис 1.67. Делитель на 1000